# Analog Switch, SPDT, 1 $\Omega$ R<sub>ON</sub>

The NLAS4157 is a low  $R_{ON}$  SPDT analog switch. This device is designed for low operating voltage, high current switching of speaker output for cell phone applications. It can switch a balanced stereo output. The NLAS4157 can handle a balanced microphone/speaker/ringtone generator in a monophone mode. The device contains a break-before-make (BBM) feature.

#### **Features**

• Single Supply Operation:

$1.65\ V$  to  $5.5\ V\ V_{CC}$  Function Directly from LiON Battery

- Tiny SC88 6-Pin Pb-Free Package:

- Meets JEDEC MO-220 Specifications

- $R_{ON}$  Typical = 0.8  $\Omega$  @  $V_{CC}$  = 4.5 V

- Low Static Power

- This is a Pb-Free Device

#### **Typical Applications**

- Cell Phone Speaker/Microphone Switching

- Ringtone-Chip/Amplifier Switching

- Stereo Balanced (Push-Pull) Switching

# **Important Information**

- Ringtone-Chip/Amplifier Switching

- Continuous Current Rating Through each Switch ±300 mA

- Conforms to: JEDEC MO-220, Issue H, Variation VEED-6

- Pin for Pin Compatible with FSA4157

# ON Semiconductor®

http://onsemi.com

SC-88 (SOT-363) CASE 419B

#### **MARKING DIAGRAM**

AN = Specific Device Code

M = Date Code\* G = Pb-Free Package

(Note: Microdot may be in either location)

\*Date Code orientation and/or position may vary depending upon manufacturing location.

#### **PIN ASSIGNMENTS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.

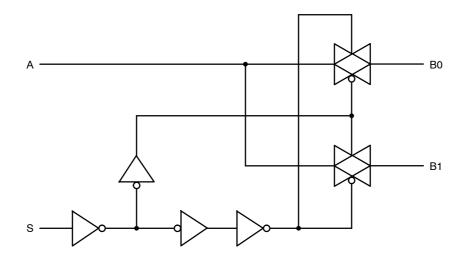

Figure 1. Input Equivalent Circuit

#### **PIN DESCRIPTION**

| Pin Name  | Description   |

|-----------|---------------|

| A, B0, B1 | Data Ports    |

| S         | Control Input |

#### **TRUTH TABLE**

| Control Input | Function          |

|---------------|-------------------|

| L             | B0 Connected to A |

| Н             | B1 Connected to A |

H = HIGH Logic Level. L = LOW Logic Level.

#### **MAXIMUM RATINGS**

| Symbol               | Rating                                                                          | Value                        | Unit |

|----------------------|---------------------------------------------------------------------------------|------------------------------|------|

| V <sub>CC</sub>      | Positive DC Supply Voltage                                                      | −0.5 to +6.0                 | V    |

| V <sub>IS</sub>      | Analog Input Voltage (V <sub>NO</sub> , V <sub>NC</sub> , or V <sub>COM</sub> ) | -0.5 to V <sub>CC</sub> +0.5 | V    |

| V <sub>IN</sub>      | Digital Select Input Voltage                                                    | −0.5 to +6.0                 | V    |

| I <sub>anl1</sub>    | Continuous DC Current from COM to NC/NO                                         | ±300                         | mA   |

| I <sub>anl-pk1</sub> | Peak Current from COM to NC/NO, 10 Duty Cycles (Note 1)                         | ±500                         | mA   |

| I <sub>clmp</sub>    | Continuous DC Current into COM/NC/NO with respect to V <sub>CC</sub> or GND     | ±100                         | mA   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Defined as 10% ON, 90% off duty cycle.

# RECOMMENDED OPERATING CONDITIONS

| Symbol                          | Rating                           | Min                                                | Max  | Unit            |      |

|---------------------------------|----------------------------------|----------------------------------------------------|------|-----------------|------|

| V <sub>CC</sub>                 | Positive DC Supply Voltage       |                                                    | 1.65 | 5.5             | V    |

| V <sub>IS</sub>                 | Analog Input Voltage (A, B0, B1) |                                                    | 0    | V <sub>CC</sub> | V    |

| V <sub>IN</sub>                 | Digital Select Input Voltage (S) |                                                    | 0    | V <sub>CC</sub> | V    |

| T <sub>A</sub>                  | Operating Temperature Range      |                                                    | -40  | 85              | °C   |

| t <sub>r</sub> , t <sub>f</sub> |                                  | V <sub>CC</sub> = 3.0 V<br>V <sub>CC</sub> = 5.5 V |      | 20<br>10        | ns/V |

#### DC ELECTRICAL CHARACTERISTICS

|                  |                                                       |                                                                       | Vcc        | T <sub>A</sub> = +25°C |     |      | T <sub>A</sub> = -40°C to +85°C |            |      |

|------------------|-------------------------------------------------------|-----------------------------------------------------------------------|------------|------------------------|-----|------|---------------------------------|------------|------|

| Symbol           | Parameter                                             | Test Conditions                                                       | (V)        | Min                    | Тур | Max  | Min                             | Max        | Unit |

| V <sub>IH</sub>  | HIGH Level<br>Input Voltage                           |                                                                       | 2.7<br>4.5 |                        |     |      | 2.0<br>2.4                      |            | V    |

| V <sub>IL</sub>  | LOW Level<br>Input Voltage                            |                                                                       | 2.7<br>4.5 |                        |     |      |                                 | 0.6<br>0.8 | V    |

| I <sub>IN</sub>  | Input Leakage Current                                 | $0 \le V_{IN} \le 5.5 V$                                              | 0-5.5      |                        |     | ±0.1 |                                 | ±1         | μΑ   |

| I <sub>OFF</sub> | OFF State Leakage<br>Current (Note 7)                 | $0 \le A, B \le V_{CC}$                                               | 5.5        | -2.0                   |     | +2.0 |                                 | ±20        | nA   |

| I <sub>ON</sub>  | ON State Leakage<br>Current (Note 7)                  | $0 \le A, B \le V_{CC}$                                               | 5.5        | -4.0                   |     | +4.0 |                                 | ±40        | nA   |

| R <sub>ON</sub>  | Switch On Resistance<br>(Note 2)                      | I <sub>O</sub> = -100 mA,<br>B <sub>0</sub> or B <sub>1</sub> = 3.5 V | 2.7        |                        | 2.0 | 4.0  |                                 | 4.3        | Ω    |

|                  |                                                       | I <sub>O</sub> = -100 mA,<br>B <sub>0</sub> or B <sub>1</sub> = 1.5 V | 4.5        |                        | 0.8 | 1.15 |                                 | 1.3        |      |

| I <sub>CC</sub>  | Quiescent Supply<br>Current<br>All Channels ON or OFF | $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$                               | 5.5        |                        |     | 0.5  |                                 | 1.0        | μΑ   |

#### **Analog Signal Range**

| ΔR <sub>ON</sub>  | On Resistance Match<br>Between Channels<br>(Notes 2, 3, 4) | $I_A = -100 \text{ mA},$ $B_0 \text{ or } B_1 = 1.5 \text{ V}$ $I_A = -100 \text{ mA},$ $B_0 \text{ or } B_1 = 3.5 \text{ V}$                                                                                                             | 2.7<br>4.5 | 0.15<br>0.12 |  | 0.15 | Ω |

|-------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--|------|---|

| R <sub>flat</sub> | On Resistance<br>Flatness (Notes 2, 3, 5)                  | $ \begin{aligned} &I_{A} = -100 \text{ mA}, \\ &B_{0} \text{ or } B_{1} = 0 \text{ V}, 0.75 \text{ V}, 1.5 \text{ V} \\ &I_{A} = -100 \text{ mA}, \\ &B_{0} \text{ or } B_{1} = 0 \text{ V}, 1.0 \text{ V}, 2.0 \text{ V} \end{aligned} $ | 2.7<br>4.5 | 1.4<br>0.3   |  | 0.4  | Ω |

<sup>2.</sup> Measured by the voltage drop between A and B pins at the indicated current through the switch. On Resistance is determined by the lower of the voltages on the two (A or B Ports).

3. Parameter is characterized but not tested in production.

4. DR<sub>ON</sub> = R<sub>ON</sub> max - R<sub>ON</sub> min measured at identical V<sub>CC</sub>, temperature and voltage levels.

5. Flatness is defined as the difference between the maximum and minimum value of On Resistance over the specified range of conditions.

<sup>6.</sup> Guaranteed by Design.

<sup>7.</sup> This parameter is guaranteed by design but not tested. The bus switch contributes no propagation delay other than the RC delay of the On Resistance of the switch and the 50 pF load capacitance, when driven by an ideal voltage source (zero output impedance).

#### **AC ELECTRICAL CHARACTERISTICS**

|                                      |                                                              |                                                                                                                                                                                                       | V <sub>CC</sub> | T,  | <sub>A</sub> = +25° | С          | T <sub>A</sub> = -40° | C to +85°C |      | Figure<br># |

|--------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|---------------------|------------|-----------------------|------------|------|-------------|

| Symbol                               | Parameter                                                    | Test Conditions                                                                                                                                                                                       | (V)             | Min | Тур                 | Max        | Min                   | Max        | Unit |             |

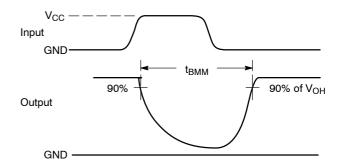

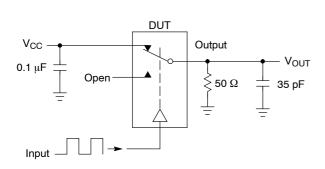

| t <sub>PHL</sub><br>t <sub>PLH</sub> | Propagation Delay<br>Bus-to-Bus (Note 9)                     | V <sub>I</sub> = OPEN                                                                                                                                                                                 | 2.7<br>4.5      |     |                     | 2.0<br>0.3 |                       |            | ns   | 3, 4        |

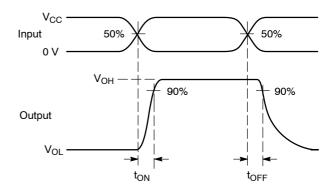

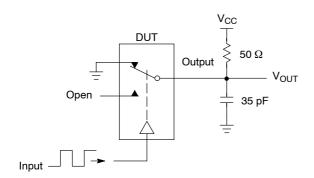

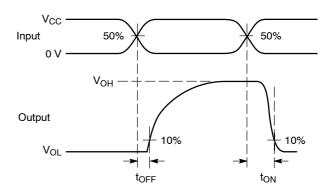

| t <sub>ON</sub>                      | Output Enable Time<br>Turn On Time<br>(A to B <sub>n</sub> ) | $\begin{array}{c} B_0 \text{ or } B_1 = 1.5 \text{ V}, \\ R_L = 50 \ \Omega, \ C_L = 35 \text{ pF} \\ B_0 \text{ or } B_1 = 3.0 \text{ V}, \\ R_L = 50 \ \Omega, \ C_L = 35 \text{ pF} \end{array}$   | 2.7<br>4.5      |     |                     | 30<br>20   |                       | 35<br>25   | ns   | 3, 4        |

| t <sub>OFF</sub>                     | Output Disable Time<br>Turn Off Time<br>(A Port to B Port)   | $\begin{array}{c} B_0 \text{ or } B_1 = 1.5 \text{V}, \\ R_L = 50 \ \Omega, \ C_L = 35 \ \text{pF} \\ B_0 \text{ or } B_1 = 3.0 \ \text{V}, \\ R_L = 50 \ \Omega, \ C_L = 35 \ \text{pF} \end{array}$ | 2.7<br>4.5      |     |                     | 20<br>15   |                       | 25<br>20   | ns   | 3, 4        |

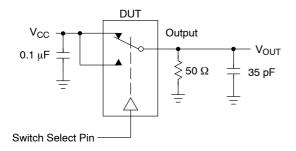

| t <sub>BBM</sub>                     | Break Before Make Time<br>(Note 8)                           |                                                                                                                                                                                                       | 2.7             | 0.5 |                     |            | 0.5                   |            | ns   | 2           |

|                                      |                                                              |                                                                                                                                                                                                       | 4.5             | 0.5 |                     |            | 0.5                   |            |      |             |

| Q                                    | Charge Injection (Note 8)                                    | $C_L$ = 1.0 nF, $V_{GEN}$ = 0 V $R_{GEN}$ = 0 $\Omega$                                                                                                                                                | 2.7<br>4.5      |     | 26<br>48            |            |                       |            | pC   | 6           |

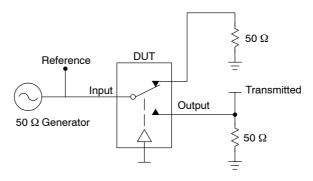

| O <sub>IRR</sub>                     | Off Isolation (Note 10)                                      | $R_L = 50 \Omega$<br>f = 1.0 MHz                                                                                                                                                                      | 2.7 –<br>5.5    |     | -52                 |            |                       |            | dB   | 5           |

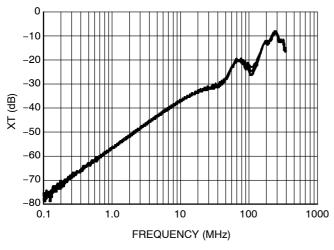

| X <sub>talk</sub>                    | Crosstalk                                                    | $R_L = 50 \Omega$<br>f = 1.0 MHz                                                                                                                                                                      | 2.7 –<br>5.5    |     | -57                 |            |                       |            | dB   | 7           |

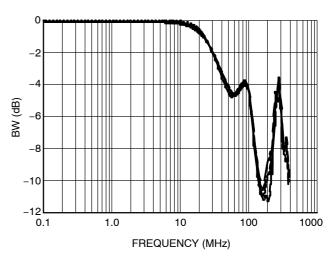

| BW                                   | -3 dB Bandwidth                                              | R <sub>L</sub> = 50 Ω                                                                                                                                                                                 | 2.7 –<br>5.5    |     | 40                  |            |                       |            | MHz  | 8           |

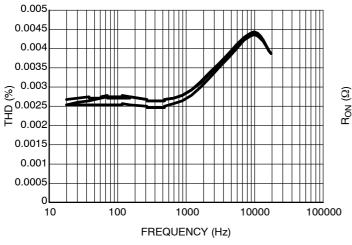

| THD                                  | Total Harmonic<br>Distortion (Note 8)                        | $R_L = 600 \Omega$<br>0.5 $V_{P-P}$<br>f = 20 Hz to 20 kHz                                                                                                                                            | 2.7 –<br>5.5    |     | 0.012               |            |                       |            | %    | 9           |

<sup>8.</sup> Guaranteed by Design.

# **CAPACITANCE** (Note 11)

| Symbol              | Parameter                                 | Test Conditions                    | Тур | Max | Unit | Figure<br># |

|---------------------|-------------------------------------------|------------------------------------|-----|-----|------|-------------|

| C <sub>IN</sub>     | Select Pin Input Capacitance              | V <sub>CC</sub> = 0 V, f = 1 MHz   | 10  |     | pF   |             |

| C <sub>IO-B</sub>   | B Port Off Capacitance                    | V <sub>CC</sub> = 4.5 V, f = 1 MHz | 25  |     | pF   |             |

| C <sub>IOA-ON</sub> | A Port Capacitance when Switch is Enabled | V <sub>CC</sub> = 4.5 V, f = 1 MHz | 87  |     | pF   |             |

<sup>11.</sup>  $T_A = +25^{\circ}C$ , f = 1 MHz, Capacitance is characterized but not tested in production.

# **DEVICE ORDERING INFORMATION**

| Device Order Number | Package            | Shipping <sup>†</sup> |

|---------------------|--------------------|-----------------------|

| NLAS4157DFT2G       | SC-88<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>9.</sup> This parameter is guaranteed by design but not tested. The bus switch contributes no propagation delay other than the RC delay of the On Resistance of the switch and the 50 pF load capacitance, when driven by an ideal voltage source (zero output impedance).

<sup>10.</sup> Off Isolation = 20  $log_{10} [V_A/V_{Bn}]$ .

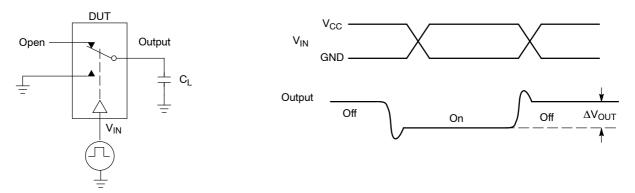

Figure 2. t<sub>BBM</sub> (Time Break-Before-Make)

Figure 3. t<sub>ON</sub>/t<sub>OFF</sub>

Figure 4.  $t_{ON}/t_{OFF}$

Channel switch control/s test socket is normalized. Off isolation is measured across an off channel. On loss is the bandwidth of an On switch.  $V_{\rm ISO}$ , Bandwidth and  $V_{\rm ONL}$  are independent of the input signal direction.

$$V_{ISO}$$

= Off Channel Isolation = 20 Log  $\left(\frac{V_{OUT}}{V_{IN}}\right)$  for  $V_{IN}$  at 100 kHz

$$V_{ONL}$$

= On Channel Loss = 20 Log  $\left(\frac{V_{OUT}}{V_{IN}}\right)$  for  $V_{IN}$  at 100 kHz to 50 MHz

Bandwidth (BW) = the frequency 3 dB below V<sub>ONL</sub>

$V_{CT}$  = Use  $V_{ISO}$  setup and test to all other switch analog input/outputs terminated with 50  $\Omega$

Figure 5. Off Channel Isolation/On Channel Loss (BW)/Crosstalk (On Channel to Off Channel)/V<sub>ONL</sub>

Figure 6. Charge Injection: (Q)

Figure 7. Cross Talk vs. Frequency

@ V<sub>CC</sub> = 4.5 V

Figure 8. Bandwidth vs. Frequency

Figure 9. Total Harmonic Distortion

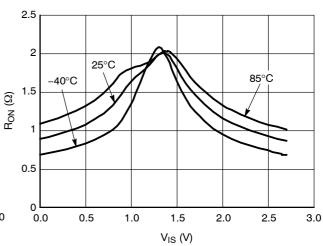

Figure 10. On–Resistance vs. Signal Voltage  $@V_{CC} = 2.7 \text{ V}$

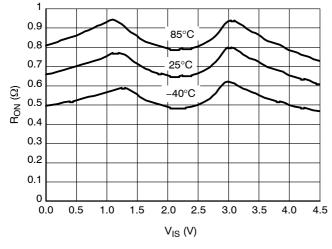

Figure 11. On–Resistance vs. Signal Voltage  $@V_{CC} = 4.5 \text{ V}$

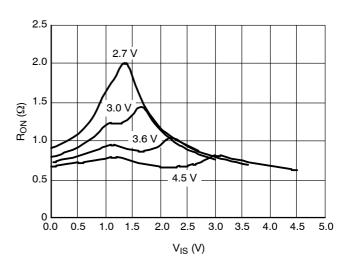

Figure 12. On-Resistance vs. Signal Voltage

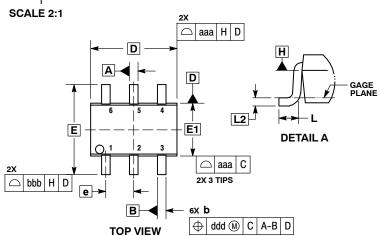

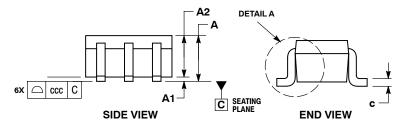

## SC-88/SC70-6/SOT-363 CASE 419B-02 **ISSUE Y**

**DATE 11 DEC 2012**

#### **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code

= Date Code\*

= Pb-Free Package

(Note: Microdot may be in either location)

- \*Date Code orientation and/or position may vary depending upon manufacturing location.

- \*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

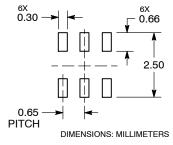

#### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42985B          | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SC-88/SC70-6/SOT-363 |                                                                                                                                               | PAGE 1 OF 2 |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.20 PER END. DIMENSIONS D AND E1 AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY AND DATUM H. DATUMS A AND B ARE DETERMINED AT DATUM H. DIMENSIONS b AND c APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.08 AND 0.15 FROM THE TIP.

- DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF DIMENSION 6 AT MAXIMUM MATERIAL CONDITION. THE DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT.

|     | MIL  | LIMETE  | ERS  |           | INCHES   | 3     |

|-----|------|---------|------|-----------|----------|-------|

| DIM | MIN  | NOM     | MAX  | MIN       | NOM      | MAX   |

| Α   |      | -       | 1.10 |           |          | 0.043 |

| A1  | 0.00 | -       | 0.10 | 0.000     |          | 0.004 |

| A2  | 0.70 | 0.90    | 1.00 | 0.027     | 0.035    | 0.039 |

| b   | 0.15 | 0.20    | 0.25 | 0.006     | 0.008    | 0.010 |

| С   | 0.08 | 0.15    | 0.22 | 0.003     | 0.006    | 0.009 |

| D   | 1.80 | 2.00    | 2.20 | 0.070     | 0.078    | 0.086 |

| E   | 2.00 | 2.10    | 2.20 | 0.078     | 0.082    | 0.086 |

| E1  | 1.15 | 1.25    | 1.35 | 0.045     | 0.049    | 0.053 |

| е   |      | 0.65 BS | С    | 0.026 BSC |          |       |

| L   | 0.26 | 0.36    | 0.46 | 0.010     | 0.014    | 0.018 |

| L2  |      | 0.15 BS | C    | (         | 0.006 BS | SC    |

| aaa | 0.15 |         |      | 0.006     |          |       |

| bbb | 0.30 |         |      | 0.012     |          |       |

| ccc |      | 0.10    |      | 0.004     |          |       |

| ddd |      | 0.10    |      |           | 0.004    |       |

# SC-88/SC70-6/SOT-363 CASE 419B-02 ISSUE Y

**DATE 11 DEC 2012**

| STYLE 1: PIN 1. EMITTER 2 2. BASE 2 3. COLLECTOR 1 4. EMITTER 1 5. BASE 1 6. COLLECTOR 2   | STYLE 2:<br>CANCELLED                                                                | STYLE 3:<br>CANCELLED                                                                     | STYLE 4: PIN 1. CATHODE 2. CATHODE 3. COLLECTOR 4. EMITTER 5. BASE 6. ANODE                       | STYLE 5:<br>PIN 1. ANODE<br>2. ANODE<br>3. COLLECTOR<br>4. EMITTER<br>5. BASE<br>6. CATHODE               | STYLE 6: PIN 1. ANODE 2 2. N/C 3. CATHODE 1 4. ANODE 1 5. N/C 6. CATHODE 2                            |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| STYLE 7: PIN 1. SOURCE 2 2. DRAIN 2 3. GATE 1 4. SOURCE 1 5. DRAIN 1 6. GATE 2             | STYLE 8:<br>CANCELLED                                                                | STYLE 9: PIN 1. EMITTER 2 2. EMITTER 1 3. COLLECTOR 1 4. BASE 1 5. BASE 2 6. COLLECTOR 2  | STYLE 10:<br>PIN 1. SOURCE 2<br>2. SOURCE 1<br>3. GATE 1<br>4. DRAIN 1<br>5. DRAIN 2<br>6. GATE 2 | STYLE 11:<br>PIN 1. CATHODE 2<br>2. CATHODE 2<br>3. ANODE 1<br>4. CATHODE 1<br>5. CATHODE 1<br>6. ANODE 2 | STYLE 12:<br>PIN 1. ANODE 2<br>2. ANODE 2<br>3. CATHODE 1<br>4. ANODE 1<br>5. ANODE 1<br>6. CATHODE 2 |

| STYLE 13:<br>PIN 1. ANODE<br>2. N/C<br>3. COLLECTOR<br>4. EMITTER<br>5. BASE<br>6. CATHODE | STYLE 14:<br>PIN 1. VREF<br>2. GND<br>3. GND<br>4. IOUT<br>5. VEN<br>6. VCC          | STYLE 15: PIN 1. ANODE 1 2. ANODE 2 3. ANODE 3 4. CATHODE 3 5. CATHODE 2 6. CATHODE 1     | STYLE 16: PIN 1. BASE 1 2. EMITTER 2 3. COLLECTOR 2 4. BASE 2 5. EMITTER 1 6. COLLECTOR 1         | STYLE 17: PIN 1. BASE 1 2. EMITTER 1 3. COLLECTOR 2 4. BASE 2 5. EMITTER 2 6. COLLECTOR 1                 | STYLE 18:<br>PIN 1. VIN1<br>2. VCC<br>3. VOUT2<br>4. VIN2<br>5. GND<br>6. VOUT1                       |

| STYLE 19:<br>PIN 1. I OUT<br>2. GND<br>3. GND<br>4. V CC<br>5. V EN<br>6. V REF            | STYLE 20: PIN 1. COLLECTOR 2. COLLECTOR 3. BASE 4. EMITTER 5. COLLECTOR 6. COLLECTOR | STYLE 21: PIN 1. ANODE 1 2. N/C 3. ANODE 2 4. CATHODE 2 5. N/C 6. CATHODE 1               | STYLE 22:<br>PIN 1. D1 (i)<br>2. GND<br>3. D2 (i)<br>4. D2 (c)<br>5. VBUS<br>6. D1 (c)            | STYLE 23:<br>PIN 1. Vn<br>2. CH1<br>3. Vp<br>4. N/C<br>5. CH2<br>6. N/C                                   | STYLE 24: PIN 1. CATHODE 2. ANODE 3. CATHODE 4. CATHODE 5. CATHODE 6. CATHODE                         |

| STYLE 25: PIN 1. BASE 1 2. CATHODE 3. COLLECTOR 2 4. BASE 2 5. EMITTER 6. COLLECTOR 1      | STYLE 26: PIN 1. SOURCE 1 2. GATE 1 3. DRAIN 2 4. SOURCE 2 5. GATE 2 6. DRAIN 1      | STYLE 27: PIN 1. BASE 2 2. BASE 1 3. COLLECTOR 1 4. EMITTER 1 5. EMITTER 2 6. COLLECTOR 2 | STYLE 28: PIN 1. DRAIN 2. DRAIN 3. GATE 4. SOURCE 5. DRAIN 6. DRAIN                               | STYLE 29:<br>PIN 1. ANODE<br>2. ANODE<br>3. COLLECTOR<br>4. EMITTER<br>5. BASE/ANODE<br>6. CATHODE        | STYLE 30:<br>PIN 1. SOURCE 1<br>2. DRAIN 2<br>3. DRAIN 2<br>4. SOURCE 2<br>5. GATE 1<br>6. DRAIN 1    |

Note: Please refer to datasheet for style callout. If style type is not called out in the datasheet refer to the device datasheet pinout or pin assignment.

| DOCUMENT NUMBER: | 98ASB42985B          | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SC-88/SC70-6/SOT-363 |                                                                                                                                                                                     | PAGE 2 OF 2 |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative