## 16-bit Single Chip Microcontroller

- Low power operation from 1.2V with a single alkaline or silver oxide button battery.

- Low power consumption standby driving at HALT 0.3 μA .

\*super economy mode

- Built-in LCD Driver: 56 SEG x 24 COM (max.)

- Internal R/F converters enable to realize various sensing.

#### DESCRIPTIONS

The S1C17W22/W23 is a 16-bit MCU that features low-voltage operation from 1.2 V even though Flash memory is included. The embedded high-efficiency DC-DC converter generates the constant-voltage to drive the IC with lower power consumption than 4-bit MCUs. This IC includes a real-time clock, a stopwatch, an LCD driver, and a PWM timer capable of being used to generate drive waveforms for a motor driver as well as a high-performance 16-bit CPU. It is suitable for battery-driven applications that require an LCD display and timers.

#### ■ FEATURES

| Model                                                               | S1C17W22                                                                              | S1C17W23                                   |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| CPU                                                                 | 101011112                                                                             | 310111120                                  |  |  |  |  |  |  |  |

| CPU core                                                            | Seiko Epson original 16-bit RISC CPU core S1C17                                       |                                            |  |  |  |  |  |  |  |

| Other                                                               | On-chip debugger                                                                      |                                            |  |  |  |  |  |  |  |

| Embedded Flash memory                                               |                                                                                       |                                            |  |  |  |  |  |  |  |

| Capacity                                                            | 64K bytes (for both instructions and data)                                            | 96K bytes (for both instructions and data) |  |  |  |  |  |  |  |

| Erase/program count                                                 | 50 times (min.) * Programming by the debu                                             |                                            |  |  |  |  |  |  |  |

| Other                                                               | Security function to protect from reading/pro                                         | ogramming by ICDmini                       |  |  |  |  |  |  |  |

|                                                                     | On-board programming function using ICDr                                              | nini                                       |  |  |  |  |  |  |  |

| Embedded RAM                                                        | ,                                                                                     |                                            |  |  |  |  |  |  |  |

| Capacity                                                            | 4K bytes                                                                              | 8K bytes                                   |  |  |  |  |  |  |  |

| Embedded display RAM                                                | 1                                                                                     | _                                          |  |  |  |  |  |  |  |

| Capacity                                                            | 576 bytes                                                                             |                                            |  |  |  |  |  |  |  |

| Clock generator (CLG)                                               | <u></u>                                                                               |                                            |  |  |  |  |  |  |  |

| System clock source                                                 | 4 sources (IOSC/OSC1/OSC3/EXOSC)                                                      |                                            |  |  |  |  |  |  |  |

| System clock frequency                                              | 1.1 MHz (max.) VDD = 1.2 to 1.6 V                                                     |                                            |  |  |  |  |  |  |  |

| (operating frequency) IOSC oscillator circuit                       | 4.2 MHz (max.) VDD = 1.6 to 3.6 V                                                     |                                            |  |  |  |  |  |  |  |

| IOSC oscillator circuit                                             | 700 kHz (typ.) embedded oscillator                                                    |                                            |  |  |  |  |  |  |  |

| (boot clock source)                                                 | 23 µs (max.) starting time (time from cancel                                          | ation of SLEEP state to vector table       |  |  |  |  |  |  |  |

|                                                                     | read by the CPU)                                                                      |                                            |  |  |  |  |  |  |  |

| OSC1 oscillator circuit                                             | 32.768 kHz (typ.) crystal oscillator                                                  |                                            |  |  |  |  |  |  |  |

|                                                                     | Oscillation stop detection circuit included                                           |                                            |  |  |  |  |  |  |  |

| OSC3 oscillator circuit                                             | 4.2 MHz (max.) crystal/ceramic oscillator                                             |                                            |  |  |  |  |  |  |  |

|                                                                     | 500 kHz, 1, 2, and 4 MHz-switchable embedded oscillator                               |                                            |  |  |  |  |  |  |  |

|                                                                     | 500 Hz to 2 MHz CR oscillator (an external                                            | R is required)                             |  |  |  |  |  |  |  |

| EXOSC clock input                                                   | 4.2 MHz (max.) square or sine wave input                                              |                                            |  |  |  |  |  |  |  |

| Other                                                               | Configurable system clock division ratio                                              |                                            |  |  |  |  |  |  |  |

|                                                                     | Configurable system clock used at wake up                                             | from SLEEP state                           |  |  |  |  |  |  |  |

|                                                                     | Operating clock frequency for the CPU and                                             | all peripheral circuits is selectable.     |  |  |  |  |  |  |  |

| I/O port (PPORT)                                                    |                                                                                       |                                            |  |  |  |  |  |  |  |

| Number of                                                           | Input/output port: 41 bits (max.)                                                     |                                            |  |  |  |  |  |  |  |

| general-purpose I/O                                                 | Output port: 1 bit (max.)                                                             |                                            |  |  |  |  |  |  |  |

| ports                                                               | Pins are shared with the peripheral I/O.                                              |                                            |  |  |  |  |  |  |  |

| Number of input                                                     | 37 bits                                                                               |                                            |  |  |  |  |  |  |  |

| interrupt ports                                                     |                                                                                       |                                            |  |  |  |  |  |  |  |

| Number of ports that                                                | 32 bits                                                                               |                                            |  |  |  |  |  |  |  |

| support                                                             | A peripheral circuit I/O function selected via software can be assigned to each port. |                                            |  |  |  |  |  |  |  |

| universal port                                                      |                                                                                       |                                            |  |  |  |  |  |  |  |

| multiplexer (UPMUX)                                                 |                                                                                       |                                            |  |  |  |  |  |  |  |

| Timers Wetchdog timer (WDT)   Congretos NMI or wetchdog timer recet |                                                                                       |                                            |  |  |  |  |  |  |  |

| Watchdog timer (WDT)                                                |                                                                                       |                                            |  |  |  |  |  |  |  |

| Real-time clock (RTCA)                                              | Theoretical regulation function for 4 accord                                          | logrestics                                 |  |  |  |  |  |  |  |

| Theoretical regulation function for 1-second correction             |                                                                                       |                                            |  |  |  |  |  |  |  |

|                                                                               | Alarm and stopwatch functions                                                                  |                                       |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|--|

| 16-bit timer (T16)                                                            | 2 channels 4 channels                                                                          |                                       |  |  |  |  |  |  |  |

| ,                                                                             | 1 channel can generate the SPIA master                                                         | Generates the SPIA master clocks      |  |  |  |  |  |  |  |

|                                                                               | clock.                                                                                         | and                                   |  |  |  |  |  |  |  |

| 40.1 // 50.4/4.//                                                             |                                                                                                | the ADC12A trigger signal.            |  |  |  |  |  |  |  |

| 16-bit PWM timer                                                              | 2 channels 3 channels                                                                          |                                       |  |  |  |  |  |  |  |

| (T16B)                                                                        | Event counter/capture function                                                                 |                                       |  |  |  |  |  |  |  |

|                                                                               | PWM waveform generation function  Number of PWM output or capture input ports: 2 ports/channel |                                       |  |  |  |  |  |  |  |

| Supply voltage detector (                                                     | Number of PWM output or capture input ports: 2 ports/channel Supply voltage detector (SVD)     |                                       |  |  |  |  |  |  |  |

| Detection level                                                               | 30 levels (1.2 to 3.6 V)                                                                       |                                       |  |  |  |  |  |  |  |

| Other                                                                         | Intermittent operation mode                                                                    |                                       |  |  |  |  |  |  |  |

|                                                                               | Generates an interrupt or reset according to                                                   | the detection level evaluation.       |  |  |  |  |  |  |  |

| Serial interfaces                                                             |                                                                                                |                                       |  |  |  |  |  |  |  |

| UART (UART)                                                                   | 1 channel                                                                                      | 2 channels                            |  |  |  |  |  |  |  |

| Complementation Control                                                       | Baud-rate generator included, IrDA1.0 supp                                                     |                                       |  |  |  |  |  |  |  |

| Synchronous Serial Interface                                                  | 1 channel<br>2 to 16-bit variable data length                                                  | 2 channels                            |  |  |  |  |  |  |  |

| (SPIA)                                                                        | The 16-bit timer (T16) can be used for the b                                                   | naud-rate generator in master mode    |  |  |  |  |  |  |  |

| 12C (I2C)                                                                     | 1 channel                                                                                      | daud-rate generator in master mode.   |  |  |  |  |  |  |  |

| 1.20 (1.20)                                                                   | Baud-rate generator included                                                                   |                                       |  |  |  |  |  |  |  |

| Sound generator (SNDA)                                                        |                                                                                                |                                       |  |  |  |  |  |  |  |

| Buzzer output function                                                        | 512 Hz to 16 kHz output frequencies                                                            |                                       |  |  |  |  |  |  |  |

| ·                                                                             | One-shot output function                                                                       |                                       |  |  |  |  |  |  |  |

| Melody generation                                                             | Pitch: 128 Hz to 16 kHz ≈ C3 to C6                                                             |                                       |  |  |  |  |  |  |  |

| function                                                                      | Duration: 7 notes/rests (Half note/rest to thi                                                 | rty-second note/rest)                 |  |  |  |  |  |  |  |

|                                                                               | Tempo: 16 tempos (30 to 480)                                                                   |                                       |  |  |  |  |  |  |  |

| ID                                                                            | Tie may be specified.                                                                          |                                       |  |  |  |  |  |  |  |

| IR remote controller (REN Number of transmitter                               | /IC)                                                                                           | 1 channel                             |  |  |  |  |  |  |  |

| channels                                                                      | _                                                                                              | 1 channel                             |  |  |  |  |  |  |  |

| LCD driver (LCD24A)                                                           |                                                                                                |                                       |  |  |  |  |  |  |  |

| LCD output                                                                    | 72 SEG × 1-8 COM (max.), 64 SEG × 9-16                                                         | 6 COM (max.) 56 SEG × 17–24 COM       |  |  |  |  |  |  |  |

| 202 oatpat                                                                    | (max.)                                                                                         | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 |  |  |  |  |  |  |  |

| LCD contrast                                                                  | 32 levels (TBD to TBD V)                                                                       |                                       |  |  |  |  |  |  |  |

| Other 1/4 or 1/3 bias power supply included, external voltage can be applied. |                                                                                                |                                       |  |  |  |  |  |  |  |

| R/F converter (RFC)                                                           |                                                                                                |                                       |  |  |  |  |  |  |  |

| Conversion method                                                             | CR oscillation type with 24-bit counters                                                       |                                       |  |  |  |  |  |  |  |

| Number of conversion                                                          | 2 channels (Up to two sensors can be conn                                                      | ected to each channel.)               |  |  |  |  |  |  |  |

| channels Supported sensors                                                    | DC-bias resistive sensors, AC-bias resistive                                                   | sensors (Ch () only)                  |  |  |  |  |  |  |  |

| 12-bit A/D converter (ADC                                                     |                                                                                                | e sensors (on only)                   |  |  |  |  |  |  |  |

| Conversion method                                                             | -                                                                                              | Successive approximation type         |  |  |  |  |  |  |  |

| Resolution                                                                    | -                                                                                              | 12 bits                               |  |  |  |  |  |  |  |

| Number of conversion                                                          | -                                                                                              | 1 channel                             |  |  |  |  |  |  |  |

| channels                                                                      |                                                                                                |                                       |  |  |  |  |  |  |  |

| Number of analog signal                                                       | -                                                                                              | 6 ports/channel                       |  |  |  |  |  |  |  |

| inputs                                                                        | (ODOME)                                                                                        |                                       |  |  |  |  |  |  |  |

| Operational amplifier/com                                                     | nparator (OPCMP)                                                                               | 2 shannels                            |  |  |  |  |  |  |  |

| Number of channels                                                            | -<br>  -                                                                                       | 2 channels                            |  |  |  |  |  |  |  |

| Multiplier/divider (COPRO Arithmetic functions                                | 16 hit x 16 hit multiplier                                                                     |                                       |  |  |  |  |  |  |  |

| Antimietic functions                                                          | 16-bit × 16-bit multiplier 16-bit × 16-bit + 32-bit multiply and accumu                        | lation unit                           |  |  |  |  |  |  |  |

|                                                                               | 32-bit ÷ 32-bit divider                                                                        | iddon dilit                           |  |  |  |  |  |  |  |

| Reset                                                                         | 1 01 3K 01 3K dividoi                                                                          |                                       |  |  |  |  |  |  |  |

| #RESET pin                                                                    | Reset when the reset pin is set to low.                                                        |                                       |  |  |  |  |  |  |  |

| Power-on reset                                                                | Reset at power on.                                                                             |                                       |  |  |  |  |  |  |  |

| Key entry reset                                                               | Reset when the P00 to P01/P02/P03 keys a                                                       | are pressed simultaneously (can be    |  |  |  |  |  |  |  |

| _                                                                             | enabled/                                                                                       |                                       |  |  |  |  |  |  |  |

| MAZ-falada C                                                                  | disabled using a register).                                                                    |                                       |  |  |  |  |  |  |  |

| Watchdog timer reset                                                          | Vatchdog timer reset Reset when the watchdog timer overflows (can be enabled/disabled using a  |                                       |  |  |  |  |  |  |  |

| Supply voltage detector                                                       | register).                                                                                     |                                       |  |  |  |  |  |  |  |

| Supply voltage detector reset                                                 | Reset when the supply voltage detector detects the set voltage level (can be enabled/          |                                       |  |  |  |  |  |  |  |

| 16361                                                                         | disabled using a register).                                                                    |                                       |  |  |  |  |  |  |  |

| Interrupt                                                                     |                                                                                                |                                       |  |  |  |  |  |  |  |

| monupe                                                                        |                                                                                                |                                       |  |  |  |  |  |  |  |

| Non-maskable interrupt | 4 systems (Reset, address misaligned interrupt, debug, NMI)              |                                           |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| Programmable interrupt | External interrupt: 1 system (8 levels)                                  |                                           |  |  |  |  |  |

|                        | Internal interrupt: 16 systems (8 levels)                                | Internal interrupt: 23 systems (8 levels) |  |  |  |  |  |

| Power supply voltage   |                                                                          |                                           |  |  |  |  |  |

| VDD operating voltage  | 1.2 to 3.6 V                                                             |                                           |  |  |  |  |  |

| VDD operating voltage  | 1.8 to 3.6 V (VPP = 7.5 V external power su                              | upply is required.)                       |  |  |  |  |  |

| for Flash programming  |                                                                          |                                           |  |  |  |  |  |

| VDD operating voltage  | 2.7 to 3.6 V                                                             |                                           |  |  |  |  |  |

| for super economy      |                                                                          |                                           |  |  |  |  |  |

| mode                   |                                                                          |                                           |  |  |  |  |  |

| Operating temperature  |                                                                          |                                           |  |  |  |  |  |

| Operating temperature  | -40 to 85 °C                                                             |                                           |  |  |  |  |  |

| range                  |                                                                          |                                           |  |  |  |  |  |

| Current consumption    | LOAFA (TDD)                                                              |                                           |  |  |  |  |  |

| SLEEP mode             | 0.15 µA (TBD)                                                            |                                           |  |  |  |  |  |

| HALT mode              | IOSC = OFF, OSC1 = OFF, OSC3 = OFF                                       |                                           |  |  |  |  |  |

| HALTINOGE              | 0.5 µA (TBD)                                                             |                                           |  |  |  |  |  |

|                        | 0.3 μA (TBD)                                                             | OSĆ1 = 32 KHz, RTC = ON                   |  |  |  |  |  |

|                        | OSC1 = 32 kHz, RTC = ON, super economy mode                              |                                           |  |  |  |  |  |

|                        | 1.5 µA (TBD)                                                             |                                           |  |  |  |  |  |

|                        | OSC1 = 32 kHz, RTC = ON, CPU = OSC1, LCD = ON (no panel load, VC2        |                                           |  |  |  |  |  |

|                        | reference,                                                               |                                           |  |  |  |  |  |

|                        | 1/3 bias), super economy mode                                            |                                           |  |  |  |  |  |

| RUN mode               | 8 µA (TBD)                                                               |                                           |  |  |  |  |  |

|                        | OSC1 = 32  kHz, RTC = ON, CPU = OSC1,                                    | FLASHCWAIT.RDWAIT[1:0] bits = 0x1         |  |  |  |  |  |

|                        | 4 μA (TBD)                                                               |                                           |  |  |  |  |  |

|                        | OSC1 = 32 kHz, RTC = ON, CPU = OSC1, super economy mode,                 |                                           |  |  |  |  |  |

|                        | FLASHCWAIT.RDWAIT[1:0] bits = 0x1                                        |                                           |  |  |  |  |  |

|                        | 250 μA (TBD)                                                             |                                           |  |  |  |  |  |

|                        | OSC3 = 1 MHz (internal oscillator), OSC1 = 32 kHz, RTC = ON, CPU = OSC3, |                                           |  |  |  |  |  |

|                        | FLASHCWAIT.RDWAIT[1:0] bits = 0x1                                        |                                           |  |  |  |  |  |

| Shipping form          | TOED45 400min (Landa Hala O. 4                                           |                                           |  |  |  |  |  |

| 1                      | TQFP15-128pin (Lead pitch: 0.4 mm)                                       |                                           |  |  |  |  |  |

| 2                      | Die form (Pad pitch: 80 µm (min.))                                       |                                           |  |  |  |  |  |

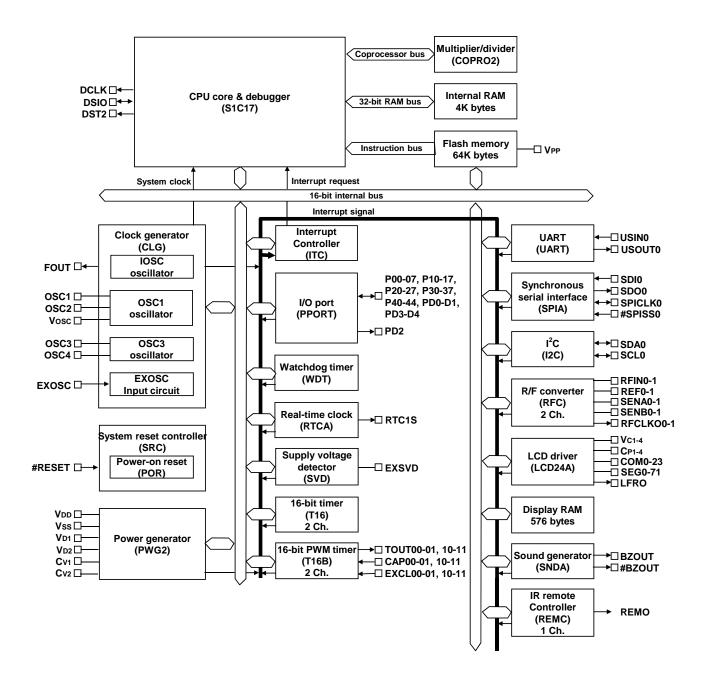

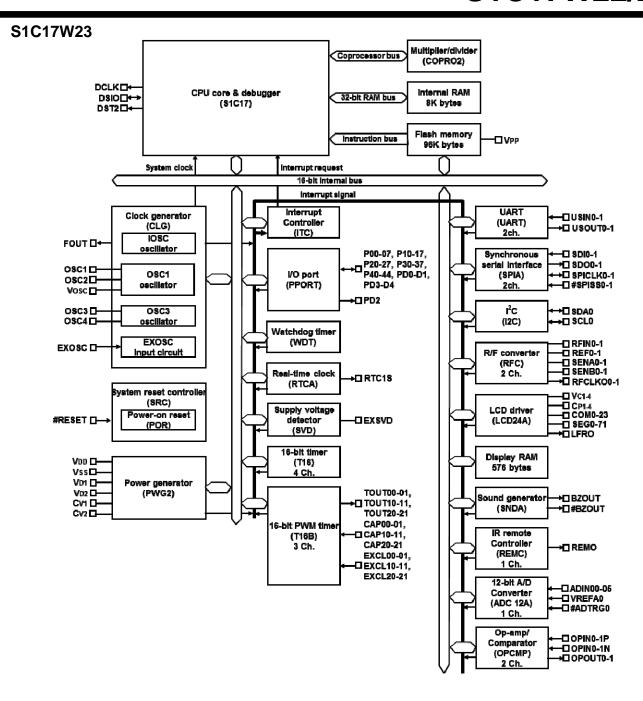

### **■ BLOCK DIAGRAM**

### S1C17W22

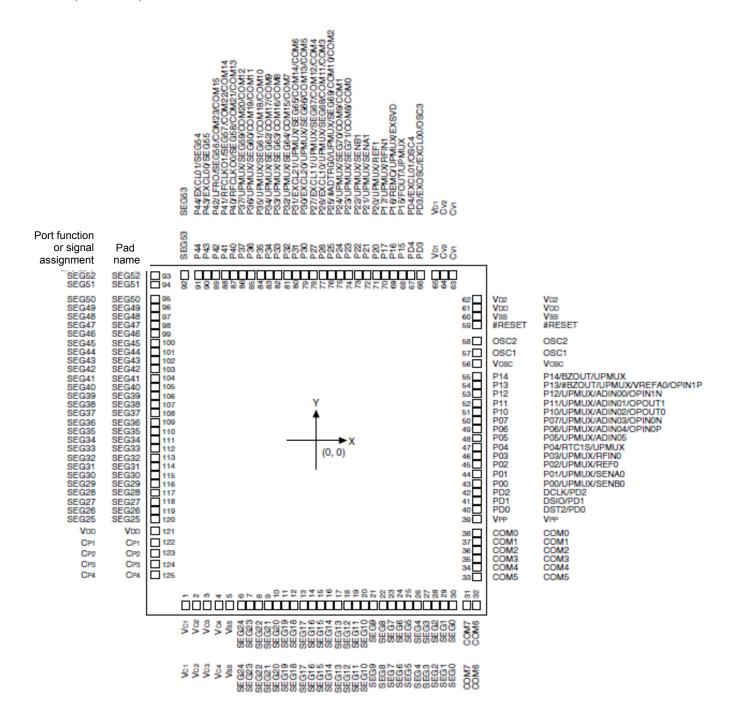

### ■ Pin Configuration Diagram

CHIP (S1C17W22) 12/00M4 11/00M3 P44/EXCL01/SEG54

P43/EXCL00/SEG56

P42/LFD/SEG56/COM23/COM15

P40/FFCLKO1/SEG57/COM22/COM14

P40/FFCLKO1/SEG57/COM21/COM13

P40/FFCLKO1/SEG57/COM21/COM13

P40/FFCLKO1/SEG57/COM21/COM13

P34/UPMUX/SEG61/COM19/COM11

P34/UPMUX/SEG61/COM19/COM10

P34/UPMUX/SEG61/COM11/COM9

P34/UPMUX/SEG61/COM11/COM9

P34/UPMUX/SEG61/COM11/COM9

P34/UPMUX/SEG61/COM11/COM19/COM10

P26/UPMUX/SEG61/COM11/COM19/COM10

P26/UPMUX/SEG61/COM11/COM19/COM10

P26/UPMUX/SEG61/COM10/COM11/COM10

P26/UPMUX/SEG61/COM10/COM11/COM10

P26/UPMUX/SEG61/COM10/COM11/COM10

P26/UPMUX/SEG61/COM10/COM11/COM10

P26/UPMUX/SEG61/UCOM10/COM11/COM10

P26/UPMUX/SEG61/UCOM10/COM11/COM10

P26/UPMUX/SEG61/UCOM10/COM11/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/COM10/ Port function PP444 PP4441 PP4 or signal assignment Pad name 93 94 SEG52 SFG52 SEG51 SEG51 288888888888888888888888888888888 SEG50 SEG50 95 96 97 98 99 100 101 102 103 104 105 106 106 107 108 62 61 Vna Vna SEG49 SEG49 VDD VDD SEG48 SEG47 SEG48 SEG47 60 59 Vss Vss #RESET #RESET SEG46 SEG45 SEG46 SEG45 OSC<sub>2</sub> OSC2 SEG44 SEG43 SEG44 57 OSC1 OSC1 SEG43 Vosc 56 Vosc SEG42 SEG42 P14/BZOUT/UPMUX 55 SEG41 SEG40 SEG41 SEG40 P13 P12 P13/#BZOUT/UPMUX P12/UPMUX 53 SEG39 SEG38 P11 P10 P07 P11/UPMUX P10/UPMUX P07/UPMUX 52 SEG38 51 50 SEG37 SEG37 SEG36 SEG35 SEG36 SEG35 49 P06 P05 P06/UPMUX P05/UPMUX | 111 | 112 | 113 | 114 | 115 | 116 | 117 | 118 | 119 | 120 48 SEG34 SEG34 P04/RTC1S/UPMUX P03/RFIN0/UPMUX 47 P04 SFG33 SEG33 (0, 0)P03 SEG32 SEG31 SEG30 SEG32 46 45 P02/REF0/UPMUX SEG31 SEG30 44 P01 P01/SENA0/UPMUX P00 P00/SENB0/UPMUX SEG29 SEG29 SEG28 43 PD2 PD1 42 DCLK/PD2 DSIO/PD1 SEG28 41 40 PDO DST2/PD0 SEG26 SEG26 SEG25 SEG25 39 \_\_121 COM0 COM1 COM2 VDD VDD COM0 38 COM1 COM2 37 36 CP1 C<sub>P1</sub> \_\_\_122 CP2 C<sub>P2</sub> **123** Die No. CJxxxxx 35 COM3 COM4 COM3 COM4 СРЗ СРЗ 124 CP4 125 CP4 COM5 COM5 32 SEG22 SEG22 SEG22 SEG32

#### CHIP (S1C17W23)

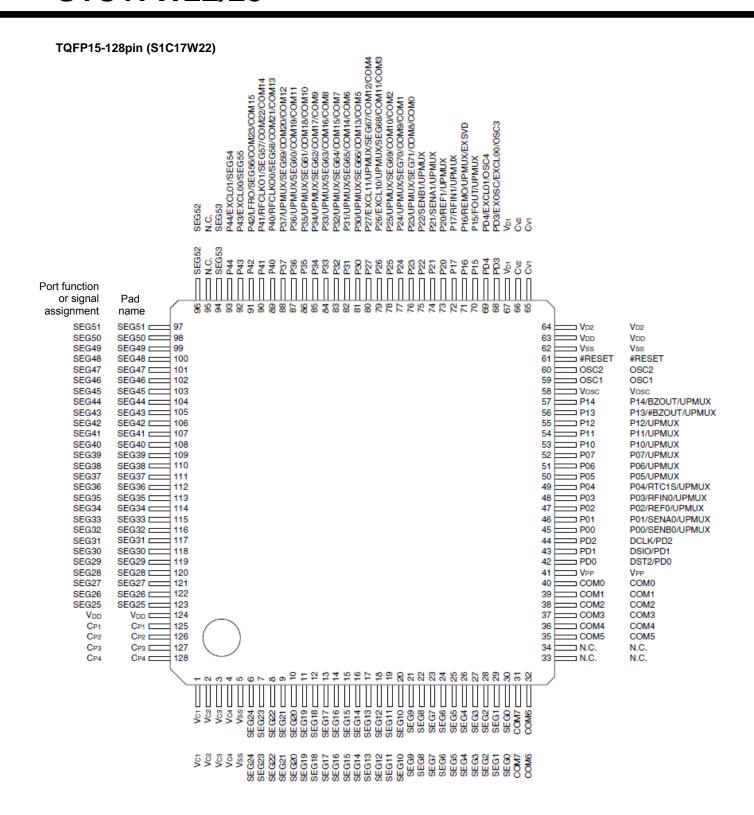

#### TQFP15-128pin (S1C17W23) PATIFICA, NOTISEGAT XONAZZOONA PATIFICA, NOTISEGAT XONAZZOONA PANIFICA, NOTISEGAS YOONA ZOONA SATUPA ULVISEGAS YOONA ZOONA SATUPA ULVISEGAS YOONA TOONA PANIFICANI STOONA TO PANIFICANI STOONA TOONA PANIFICA ZAUPA ULXISEGAS CONTISCONA TAOONA PANIFICA ZAUPA ULXISEGAS CONTISCONA SATUPA ULXISEGAS CONTISCONA SATUPA ULXISEGAS CONTISCONA PANIFICA ZAUPA ULXISEGAS CONTISCONA PANIFICA ZAUPA ULXISEGAS CONTISCONA PANIFICA ZAUPA ULXISEGAS CONTISCONA PANIFICA ZAUPA ULXISEGAS CONTISCONA PANIFICA TAUPA ULXISEGAS CONTISCONA PANIFICA TAUPA ULXISEGAS TA CONA SOONA PANIFICA TAUPA ULXISEGAS TA CONA SOONA PANIFICANI TA CONA SOONA TA CO Port function or signal Pad assignment name SEG54 SEGM F 97 T Vns Voo SEG49 SEG49 \_\_\_\_\_ 99 62 Vss Vss Vss SEG48 SEG48 100 #RESET #RESET SEG47 101 SEG47 60 OSC2 OSC2 SEG46 SEG45 SEG46 SEG45 102 OSC1 58 Vosc Vosc P14/BZOUT/UPMUX P13/#BZOUT/UPMUX/VREFA0/OPIN1P P12/UPMUX/ADIN00/OPIN1N SEG44 SEG44 104 105 □ P14 SEG43 SEG43 **=**P13 SEG42 SEG42 106 55 P12 SEG41 SEG41 P11/UPMUX/ADIN01/OPOUT SEG40 53 52 P10/UPMUX/ADIN02/OPOUT0 P07/UPMUX/ADIN03/OPIN0N P06/UPMUX/ADIN04/OPIN0P 108 □ P10 □ P07 SEG40 SEG39 109 SEG38 SEG38 110 51 ■ P06 P05 P05/UPMUX/ADIN05 P04/RTC1S/UPMUX SEG37 50 49 SEG36 SEG36 112 P03/UPMUX/RFIN0 P02/UPMUX/REF0 P01/UPMUX/SENA0 SEG35 ==== — P03 — P02 SEG35 113 114 SEG34 SEG33 SEG33 115 46 \_\_\_ P01 SEG32 SEG32 = P00 P00/UPMUX/SENB0 SEG31 117 44 PD2 DCLK/PD2 42 SEG29 SEG29 119 $\neg PD0$ DST2/PD0 SEG28 = 120 121 VPP COM0 Vpp COM0 SEG28 SEG27 SEG26 SEG26 c 122 39 38 □ COM1 COM1 SEG25 123 COM2 COM2 VDD CP1 CP2 CP3 VDD CP1 124 125 COM3 37 36 COM3 COM4 COME N.C. N.C. CP₂ = 126 35 COM5 127 N.C.

### **■** Pin Descriptions

**Symbol meanings**

Assigned signal: The signal listed at the top of each pin is assigned in the initial state. The pin function must

be switched via software to assign another signal (see the "I/O Ports" chapter).

I/O: I = Input O = Output

O = Output

I/O = Input/output

P = Power supply

A = Analog signal

Hi-Z = High impedance state

Initial state: I (Pull-up) = Input with pulled up

I (Pull-down) = Input with pulled down

Hi-Z = High impedance state

O (H) = High level output

O (L) = Low level output

Tolerant fail-safe structure:

= Over voltage tolerant fail-safe type I/O cell included

(see the "I/O Ports" chapter)

| Pin/pad<br>name | Assigned signal | I/O | Initial<br>state | Tolerant fail-safe structure | Function                                                      |  |

|-----------------|-----------------|-----|------------------|------------------------------|---------------------------------------------------------------|--|

| VDD             | VDD             | Р   | _                | -                            | Power supply (+)                                              |  |

| VSS             | VSS             | Р   | _                | -                            | GND                                                           |  |

| VPP             | VPP             | Р   | _                | _                            | Power supply for Flash programming                            |  |

| VD1             | VD1             | Α   | _                | _                            | DC-DC converter output                                        |  |

| VD2             | VD2             | Α   | _                | _                            | DC-DC converter stabilization capacitor connect pin           |  |

| CV1-2           | CV1-2           | Α   | _                | _                            | DC-DC converter charge pump capacitor connect pins            |  |

| VC1-4           | VC1-4           | P   | _                | _                            | LCD panel driver power supply                                 |  |

| CP1-4           | CP1-4           | Α   | _                | _                            | LCD power supply booster capacitor connect pins               |  |

| VOSC            | VOSC            | Α   | _                | _                            | OSC1 oscillator circuit voltage regulator output              |  |

| OSC1            | OSC1            | Α   | _                | _                            | OSC1 oscillator circuit input                                 |  |

| OSC2            | OSC2            | A   | _                | _                            | OSC1 oscillator circuit output                                |  |

| #RESET          | #RESET          | 1   | I (Pull-up)      | _                            | Reset input                                                   |  |

| P00             | P00             | 1/0 | Hi-Z             | _                            | I/O port                                                      |  |

| . 00            | UPMUX           | 1/0 |                  |                              | User-selected I/O (universal port multiplexer)                |  |

|                 | SENB0           | A   |                  |                              | R/F converter Ch.0 sensor B oscillator pin                    |  |

| P01             | P01             | 1/0 | Hi-Z             | _                            | I/O port                                                      |  |

| 101             | UPMUX           | 1/0 | 1112             |                              | User-selected I/O (universal port multiplexer)                |  |

|                 | SENA0           | A   |                  |                              | R/F converter Ch.0 sensor A oscillator pin                    |  |

| P02             | P02             | 1/0 | Hi-Z             | _                            | I/O port                                                      |  |

| 1 02            | UPMUX           | 1/0 | 111-2            | _                            | User-selected I/O (universal port multiplexer)                |  |

|                 | REF0            | A   |                  |                              | R/F converter Ch.0 reference oscillator pin                   |  |

| P03             | P03             | 1/0 | Hi-Z             |                              | I/O port                                                      |  |

| F03             | UPMUX           | 1/0 | 111-2            | _                            | User-selected I/O (universal port multiplexer)                |  |

|                 | RFIN0           | A   |                  |                              | R/F converter Ch.0 oscillation input                          |  |

| P04             | P04             | I/O | Hi-Z             | 1                            | I/O port                                                      |  |

| 1 04            | RTC1S           | 0   | 111-2            | •                            | Real-time clock 1-second cycle pulse output                   |  |

|                 | UPMUX           | 1/0 |                  |                              | User-selected I/O (universal port multiplexer)                |  |

| P05             | P05             | 1/0 | Hi-Z             |                              | I/O port                                                      |  |

| F03             | UPMUX           | 1/0 | ПІ-Д             | _                            | User-selected I/O (universal port multiplexer)                |  |

|                 | ADIN05          | 1/O |                  |                              | 12-bit A/D converter Ch.0 analog signal input 5               |  |

|                 | ADINOS          | _ ^ |                  |                              | (S1C17W23 only)                                               |  |

| P06             | P06             | I/O | Hi-Z             |                              | I/O port                                                      |  |

| 1 00            | UPMUX           | 1/0 | 111-2            | _                            | User-selected I/O (universal port multiplexer)                |  |

|                 | ADIN04          | A   |                  |                              | 12-bit A/D converter Ch.0 analog signal input 4               |  |

|                 | ADINOT          | _ ^ |                  |                              | (S1C17W23 only)                                               |  |

|                 | OPIN0P          | Α   |                  |                              | Operational amplifier/comparator Ch.0 analog signal input (+) |  |

|                 | OI IIVOI        |     |                  |                              | (S1C17W23 only)                                               |  |

| P07             | P07             | I/O | Hi-Z             | _                            | I/O port                                                      |  |

| 1 07            | UPMUX           | 1/0 | 111-2            |                              | User-selected I/O (universal port multiplexer)                |  |

|                 | ADIN03          | A   |                  |                              | 12-bit A/D converter Ch.0 analog signal input 3               |  |

|                 | ADINOS          | _ ^ |                  |                              | (S1C17W23 only)                                               |  |

|                 | OPIN0N          | Α   |                  |                              | Operational amplifier/comparator Ch.0 analog signal input (-) |  |

|                 | 31 114014       |     |                  |                              | (S1C17W23 only)                                               |  |

| P10             | P10             | I/O | Hi-Z             |                              | I/O port                                                      |  |

| . 10            | UPMUX           | 1/0 | 111-2            |                              | User-selected I/O (universal port multiplexer)                |  |

|                 | ADIN02          | A   |                  |                              | 12-bit A/D converter Ch.0 analog signal input 2               |  |

|                 | , (DII 402      |     |                  |                              | (S1C17W23 only)                                               |  |

|                 | OPOUT0          | Α   | 1                |                              | Operational amplifier/comparator Ch.0 analog signal output    |  |

|      |                |            |       |   | (S1C17W23 only)                                                                           |

|------|----------------|------------|-------|---|-------------------------------------------------------------------------------------------|

| P11  | P11            | I/O        | Hi-Z  | _ | I/O port                                                                                  |

|      | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

| 1    | ADIN01         | Α          |       |   | 12-bit A/D converter Ch.0 analog signal input 1                                           |

|      |                |            |       |   | (S1C17W23 only)                                                                           |

|      | OPIOUT1        | Α          |       |   | Operational amplifier/comparator Ch.1 analog signal output                                |

|      |                |            |       |   | (S1C17W23 only)                                                                           |

| P12  | P12            | I/O        | Hi-Z  | _ | I/O port                                                                                  |

| 1    | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

| 1    | ADIN00         | Α          |       |   | 12-bit A/D converter Ch.0 analog signal input 0                                           |

| 1    | OPIN1N         | Α          |       |   | (S1C17W23 only)  Operational amplifier/comparator Ch.1 analog signal input (-)            |

| 1    | OFININ         | A          |       |   | (S1C17W23 only)                                                                           |

| P13  | P13            | I/O        | Hi-Z  | _ | I/O port                                                                                  |

|      | #BZOUT         | 0          |       |   | Sound generator inverted output                                                           |

| 1    | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | VREFA0         | Α          |       |   | 12-bit A/D converter Ch.0 reference voltage input                                         |

|      |                |            |       |   | (S1C17W23 only)                                                                           |

|      | OPIN1P         | Α          |       |   | Operational amplifier/comparator Ch.1 analog signal input (+)                             |

|      |                |            |       |   | (S1C17W23 only)                                                                           |

| P14  | P14            | I/O        | Hi-Z  | _ | I/O port                                                                                  |

| 1    | BZOUT          | 0          |       |   | Sound generator output                                                                    |

| P15  | UPMUX<br>P15   | I/O<br>I/O | Hi-Z  | , | User-selected I/O (universal port multiplexer)  I/O port                                  |

| P 15 | FOUT           | 0          | ⊓I-Z  | ✓ | Clock external output                                                                     |

| 1    | UPMUX          | 1/0        |       |   | User-selected I/O (universal port multiplexer)                                            |

| P16  | P16            | 1/0        | Hi-Z  | _ | I/O port                                                                                  |

|      | REMO           | 0          |       |   | IR remote controller transmit data output                                                 |

|      | UPMUX          | 1/0        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | EXSVD          | A          |       |   | External power supply voltage detection input                                             |

| P17  | P17            | I/O        | Hi-Z  | 1 | I/O port                                                                                  |

| 1    | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | RFIN1          | Α          |       |   | R/F converter Ch.1 oscillation input                                                      |

| P20  | P20            | I/O        | Hi-Z  | ✓ | I/O port                                                                                  |

|      | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

| L    | REF1           | A          |       |   | R/F converter Ch.1 reference oscillator pin                                               |

| P21  | P21            | 1/0        | Hi-Z  | ✓ | I/O port                                                                                  |

|      | UPMUX<br>SENA1 | I/O<br>A   |       |   | User-selected I/O (universal port multiplexer) R/F converter Ch.1 sensor A oscillator pin |

| P22  | P22            | I/O        | Hi-Z  | 1 | I/O port                                                                                  |

| 1 22 | UPMUX          | 1/0        | 111-2 | • | User-selected I/O (universal port multiplexer)                                            |

|      | SENB1          | A          |       |   | R/F converter Ch.1 sensor B oscillator pin                                                |

| P23  | P23            | I/O        | Hi-Z  | / | I/O port                                                                                  |

| 1    | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | SEG71          | Α          |       |   | LCD segment output                                                                        |

|      | COM8/COM0      | Α          |       |   | LCD COMMON OUTPUT                                                                         |

| P24  | P24            | I/O        | Hi-Z  | ✓ | I/O port                                                                                  |

|      | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

| 1    | SEG70          | Α          |       |   | LCD segment output                                                                        |

| DOE  | COM9/COM1      | A          | 11: 7 | , | LCD COMMON OUTPUT                                                                         |

| P25  | P25<br>#ADTRG0 | I/O        | Hi-Z  | / | I/O port  12-bit A/D converter Ch.0 trigger input (S1C17W23 only)                         |

| 1    | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | SEG69          | A          |       |   | LCD segment output                                                                        |

|      | COM10/COM2     | A          |       |   | LCD COMMON OUTPUT                                                                         |

| P26  | P26            | I/O        | Hi-Z  | / | I/O port                                                                                  |

|      | EXCL10         | I          |       | _ | 16-bit PWM timer Ch.1 event counter input 0                                               |

|      | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | SEG68          | Α          |       |   | LCD segment output                                                                        |

|      | COM11/COM3     | Α          |       |   | LCD COMMON OUTPUT                                                                         |

| P27  | P27            | I/O        | Hi-Z  | ✓ | I/O port                                                                                  |

|      | EXCL11         | 1          |       |   | 16-bit PWM timer Ch.1 event counter input 1                                               |

|      | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | SEG67          | A          |       |   | LCD segment output                                                                        |

| P30  | COM12/COM4     | A<br>I/O   | 11: 7 | , | LCD COMMON OUTPUT                                                                         |

| P30  | P30<br>EXCL20  | I/O        | Hi-Z  | ✓ | I/O port 16-bit PWM timer Ch.2 event counter input 0 (S1C17W23                            |

|      | LAGLZU         | '          |       |   | only)                                                                                     |

|      | UPMUX          | I/O        |       |   | User-selected I/O (universal port multiplexer)                                            |

|      | SEG66          | A          |       |   | LCD segment output                                                                        |

| •    |                |            | i     | İ |                                                                                           |

| P31  | COM13/COM5     | A<br>I/O   | Hi-Z  |   | LCD COMMON OUTPUT  I/O port                                                               |

|         | EVOL04      |          | I           |          | 4C hit DMM times Ch 2 avent acceptanism to 4 (C4C47)MO2     |  |

|---------|-------------|----------|-------------|----------|-------------------------------------------------------------|--|

|         | EXCL21      | ı        |             |          | 16-bit PWM timer Ch.2 event counter input 1 (S1C17W23 only) |  |

|         | UPMUX       | I/O      | 1           |          | User-selected I/O (universal port multiplexer)              |  |

|         | SEG65       | A        |             |          | LCD segment output                                          |  |

|         | COM14/COM6  | A        | 1           |          | LCD COMMON OUTPUT                                           |  |

| P32     | P32         | 1/0      | Hi-Z        | <b>✓</b> | I/O port                                                    |  |

|         | UPMUX       | I/O      |             | •        | User-selected I/O (universal port multiplexer)              |  |

|         | SEG64       | A        |             |          | LCD segment output                                          |  |

|         | COM15/COM7  | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P33     | P33         | I/O      | Hi-Z        | /        | I/O port                                                    |  |

| . 55    | UPMUX       | I/O      | 1           | •        | User-selected I/O (universal port multiplexer)              |  |

|         | SEG63       | A        |             |          | LCD segment output                                          |  |

|         | COM16/COM8  | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P34     | P34         | I/O      | Hi-Z        | /        | I/O port                                                    |  |

|         | UPMUX       | I/O      | 1 –         | •        | User-selected I/O (universal port multiplexer)              |  |

|         | SEG62       | A        |             |          | LCD segment output                                          |  |

|         | COM17/COM9  | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P35     | P35         | I/O      | Hi-Z        | /        | I/O port                                                    |  |

| . 55    | UPMUX       | I/O      | 1           | •        | User-selected I/O (universal port multiplexer)              |  |

|         | SEG61       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

|         | COM18/COM10 | Α        |             |          | LCD COMMON OUTPUT                                           |  |

| P36     | P36         | 1/0      | Hi-Z        | <b>✓</b> | I/O port                                                    |  |

| . 55    | UPMUX       | I/O      | 1           | •        | User-selected I/O (universal port multiplexer)              |  |

|         | SEG60       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

|         | COM19/COM11 | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P37     | P37         | 1/0      | Hi-Z        | /        | I/O port                                                    |  |

|         | UPMUX       | I/O      | · · · · -   | v        | User-selected I/O (universal port multiplexer)              |  |

|         | SEG59       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

|         | COM20/COM12 | A        | 1           |          | LCD COMMON OUTPUT                                           |  |

| P40     | P40         | 1/0      | Hi-Z        | /        | I/O port                                                    |  |

| 1 40    | RFCLKO0     | 0        | 12          | •        | R/F converter Ch.0 clock monitor output                     |  |

|         | SEG58       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

|         | COM21/COM13 | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P41     | P41         | 1/0      | Hi-Z        | /        | I/O port                                                    |  |

| 1 71    | RFCLKO1     | 0        | 1 2         | v        | R/F converter Ch.1 clock monitor output                     |  |

|         | SEG57       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

|         | COM22/COM14 | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P42     | P42         | 1/0      | Hi-Z        | /        | I/O port                                                    |  |

| 1 72    | LFRO        | 0        | 111-2       | •        | LCD frame signal monitor output                             |  |

|         | SEG56       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

|         | COM23/COM15 | A        |             |          | LCD COMMON OUTPUT                                           |  |

| P43     | P43         | 1/0      | Hi-Z        | /        | I/O port                                                    |  |

| 1 43    | EXCL00      | 1/0      | 111-2       | •        | 16-bit PWM timer Ch.0 event counter input 0                 |  |

|         | SEG55       | A        |             |          | LCD SEGMENT OUTPUT                                          |  |

| P44     | P44         | 1/0      | Hi-Z        | ,        | I/O port                                                    |  |

| 1       | EXCL01      | 1        | 111-2       | ✓        | 16-bit PWM timer Ch.0 event counter input 1                 |  |

|         | SEG54       | A        | 1           |          | LCD SEGMENT OUTPUT                                          |  |

| PD0     | DST2        | 0        | O (L)       | <b>√</b> | On-chip debugger status output                              |  |

| 1 50    | PD0         | 1/0      | J (L)       | <b>,</b> | I/O port                                                    |  |

| PD1     | DSIO        | 1/0      | I (Pull-up) | ,        | On-chip debugger status output                              |  |

| ן רטו   | PD1         | 1/0      | i (Full-up) | ✓        | I/O port                                                    |  |

| PD2     | DCLK        | 0        | O (H)       | ,        | On-chip debugger status output                              |  |

| FDZ     | PD2         | 0        | U (n)       | ✓        | I/O port                                                    |  |

| PD3     | PD2<br>PD3  | 1/0      | Hi-Z        |          | I/O port                                                    |  |

| PDS     |             | 1/0      | □ -∠        | _        |                                                             |  |

|         | EXOSC       | <u> </u> | -           |          | Clock generator external clock input                        |  |

|         | EXCL00      | I        | -           |          | 16-bit PWM timer Ch.0 event counter input 0                 |  |

| DD4     | OSC3        | A        | 11: 7       |          | OSC3 oscillator circuit input                               |  |

| PD4     | PD4         | 1/0      | Hi-Z        | _        | I/O port                                                    |  |

|         | EXCL01      | l<br>^   | -           |          | 16-bit PWM timer Ch.0 event counter input 1                 |  |

| COMO 7  | OSC4        | A        | 11: 7       |          | OSC3 oscillator circuit output                              |  |

| COM0-7  | COM0-7      | A        | Hi-Z        | _        | LCD COMMON OUTPUT                                           |  |

| SEG0-53 | SEG0-53     | Α        | Hi-Z        | -        | LCD SEGMENT OUTPUT                                          |  |

Notes:

<sup>·</sup> In the peripheral circuit descriptions, the assigned signal name is used as the pin name.

<sup>·</sup> Both the S1C17W23 A/D converter and operational amplifier/comparator pins are assigned to the same pin function.

#### **Universal port multiplexer (UPMUX)**

The universal port multiplexer (UPMUX) allows software to select the peripheral circuit input/output function to be assigned to each pin from those listed below.

| Peripheral circuit | Signal to be assigned | I/O | Channel number n             | Function                             |

|--------------------|-----------------------|-----|------------------------------|--------------------------------------|

| Synchronous serial | SDI <i>n</i>          | I   | S1C17W22: n = 0              | SPIA Ch.n data input                 |

| interface          | SDO <i>n</i>          | 0   | S1C17W23: n = 0, 1           | SPIA Ch.n data output                |

| (SPIA)             | SPICLK <i>n</i>       | I/O |                              | SPIA Ch.n clock input/output         |

|                    | #SPISSn               | I   |                              | SPIA Ch.n slave-select input         |

| I2C                | SCL <i>n</i>          | I/O | S1C17W22: n = 0              | I2C Ch.n clock input/output          |

| (I2C)              | SDA <i>n</i>          | I/O | S1C17W23: n = 0              | I2C Ch.n data input/output           |

| UART               | USIN <i>n</i>         | I   | S1C17W22: n = 0              | UART Ch.n data input                 |

| (UART)             | USOUT <i>n</i>        | 0   | S1C17W23: n = 0, 1           | UART Ch.n data output                |

| 16-bit PWM timer   | TOUTn0/CAPn0          | I/O | S1C17W22: n = 0, 1           | T16B Ch.n PWM output/capture input 0 |

| (T16B)             | TOUTn1/CAPn1          | I/O | S1C17W23: <i>n</i> = 0, 1, 2 | T16B Ch.n PWM output/capture input 1 |

Note: Do not assign a function to two or more pins simultaneously.

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies. ©Seiko Epson Corporation 2013, All rights reserved

### SEIKO EPSON CORPORATION

**MICRODEVICES OPERATIONS DIVISION**

IC Sales & Marketing Department 421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-42-587-5814 FAX: +81-42-587-5117 EPSON semiconductor website

http://www.epson.jp/device/semicon\_e/

Document code: 412533601 First issue Nov., 2012 in Japan Revised Jun., 2013